我院教师在集成电路领域国际权威期刊《IEEE Transactions on Circuits and SystemI: Regular Papers》上连续发表研究成果

发布时间:2026-01-22 14:04:30

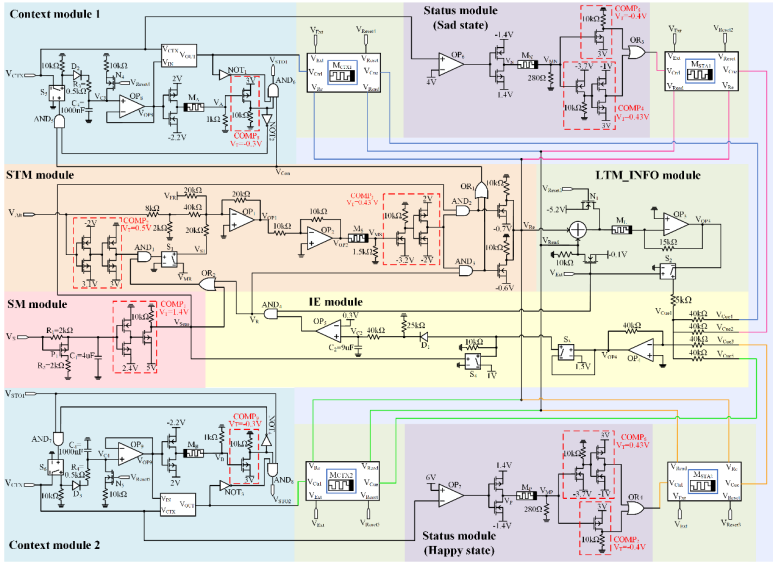

将记忆信息的三级加工模型与人类记忆机制相结合,实现了一种具有情境依赖和状态依赖的忆阻脑启发记忆电路,如图所示。该电路具有感知、编码、可变学习和遗忘率、巩固、检索以及复位控制等丰富功能,具有很强的可扩展性,能实现多情境下信息记忆。另外,该电路实现了感觉记忆、短时记忆、长时记忆三种记忆共存,并兼顾了影响信息检索的多种因素,如信息的记忆程度、信息记忆与信息检索的时间间隔、情境及状态,对类脑人工智能硬件发展具有重要意义。

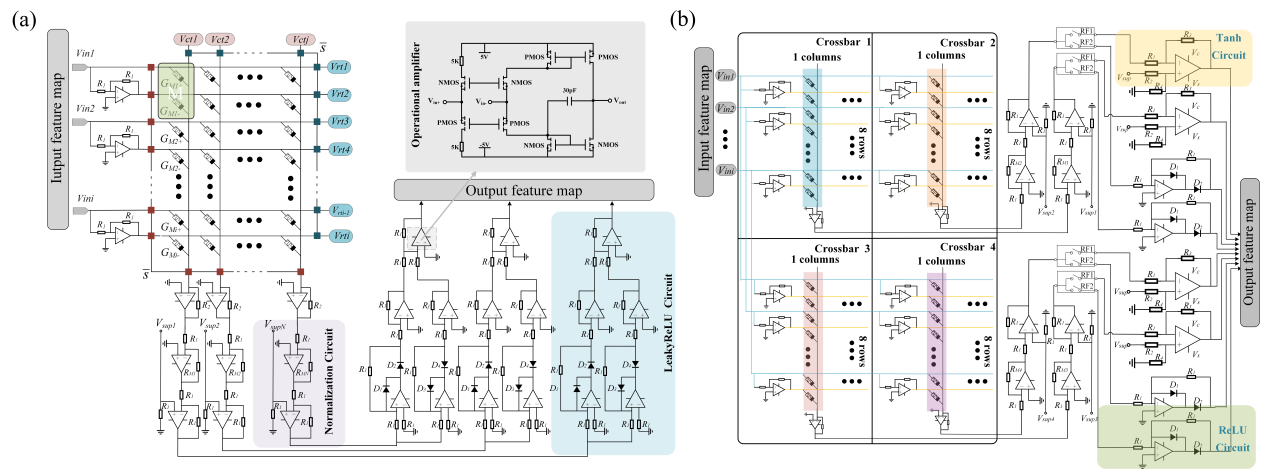

基于忆阻器阵列实现了一种由基于卷积神经网络的判别器和基于反卷积神经网络的生成器构成的深度卷积生成对抗网络(DCGAN)架构(如图2所示),为在边缘设备上实现AI计算提供一种全新方案。与传统DCGAN相比,该架构能以更高的稳定性、更低的复杂度和能耗实现边缘计算。Oxford 17图像生成任务中,在保持面积开销不变的情况下,该架构将时间消耗减少了80%,能耗降低了78%。

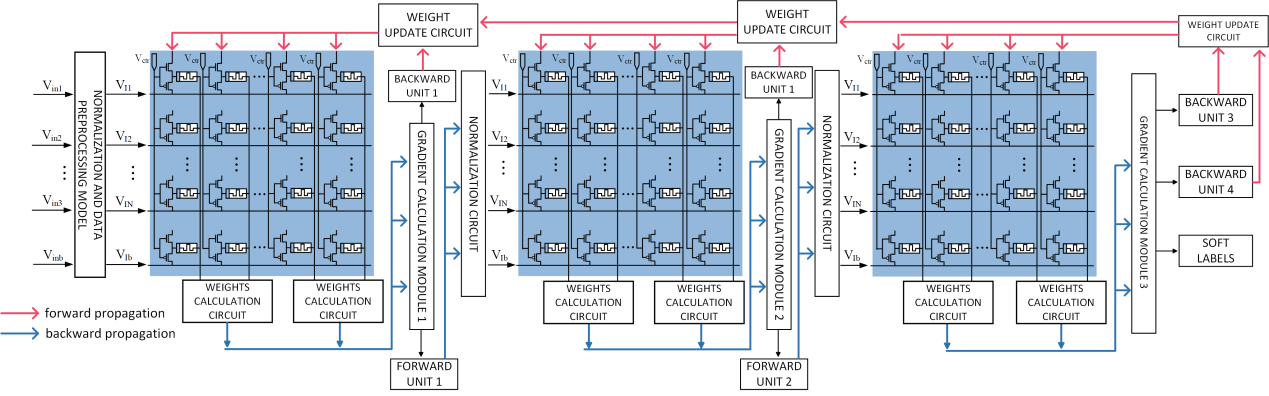

基于忆阻器交叉阵列实现了一种知识蒸馏在线训练电路架构,旨在提高边缘设备上深度学习的推理效率并降低能耗,如图3所示。该电路架构能够利用忆阻交叉阵列高效更新权重和计算,进行实时数据处理。该架构克服了在复杂深度神经网络中传统故障检测方法的低效问题,短时间内同时检测区域内所有忆阻器件,极大提高故障检测效率。通过结合区域检测方案,电路在故障条件下的模型训练和推理能力得到显著提高,展示了其在边缘计算电路故障检测中的潜力和优势。

近年来,窦刚老师课题组响应国家人工智能和集成电路发展战略,基于感存算一体的新型计算架构,从忆阻器制备到类脑智能信息处理硬件系统,成功实现“神经机制-智能算法-硬件架构”三位一体的技术突破,多项成果已发表于IEEE TFS、TCAS-I、TBioCAS、APL等国际权威期刊。